In the semiconductor industry, we often find ourselves caught between two worlds: the infinitesimal realm of quantum mechanics and the high-stakes theater of global business. For executives, the focus is on yield, power budgets and market competitiveness. For engineers, the daily grind involves managing dangling bonds and oxide disorders.

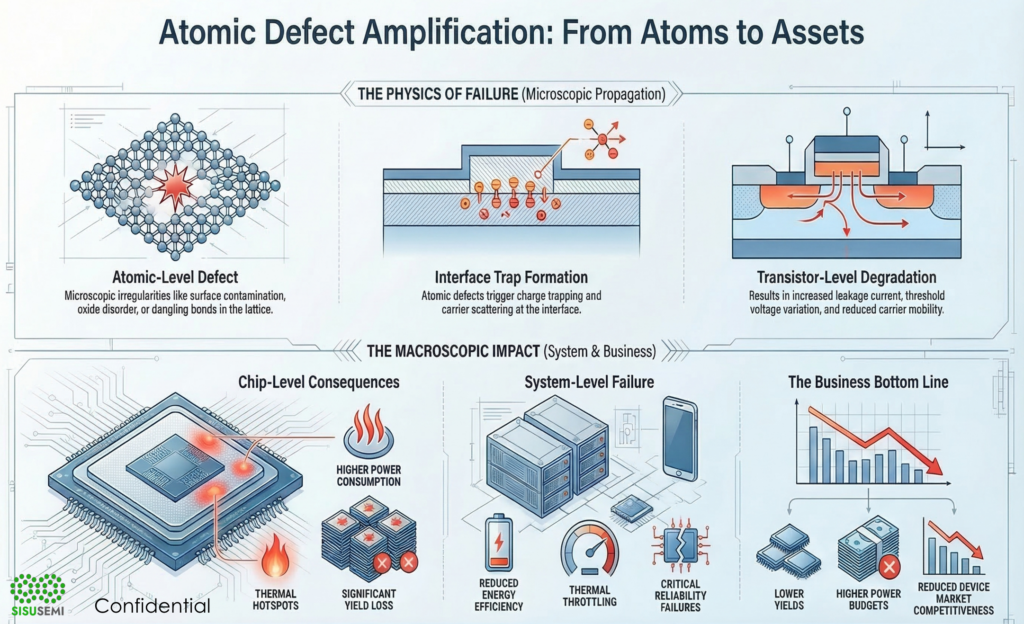

The bridge between these two worlds is often foggy. How exactly does a single misplaced atom in a silicon lattice translate into a missed quarterly shipment or a product recall? To solve this communication gap, we use the atomic defect amplification diagram. This framework provides a clear roadmap from atomic physics to system-level impact, ensuring that everyone from the cleanroom to the boardroom understands the why behind device failure.

1. The root cause: Atomic-level defects

It all starts at the surface. Whether it is surface contamination, a dangling bond, oxide disorder or a simple atomic impurity, these microscopic anomalies are the root causes of chip failure. In a perfect crystal, electrons flow predictably. However, these defects disrupt that harmony, creating the foundation for the cascade that follows.

2. The chain reaction: Interface trap formation

Once an atomic defect is present, it manifests physically as an interface trap. This stage is where the amplification truly begins. These traps lead to:

- Charge trapping: Electrons or holes become stuck, altering the electrical environment.

- Carrier scattering: The physical path of the charge carriers is disrupted, much like a car hitting a pothole on a highway.

These are not just theoretical physics problems; they are the direct precursors to measurable transistor degradation.

3. Transistor-level and device-level impact

As these traps accumulate, the individual transistor begins to struggle. We start seeing increased leakage current, significant threshold voltage () variation and reduced carrier mobility.

At the device level, this translates to:

- Slower switching speeds: The transistor can’t turn on or off as fast as the design requires.

- Increased static power: Even when the device is off, it’s still bleeding energy.

- Reliability degradation: The device effectively ages faster than intended.

4. The macro scale: Chip and system consequences

When millions—or billions—of these compromised transistors are packed onto a single die, the problem scales exponentially. We no longer talk about traps; we talk about thermal hotspots, reduced performance and yield loss.

By the time the silicon reaches the system level (your smartphone or a server farm), the defect has amplified into:

- Thermal throttling: The system must slow down to avoid melting itself.

- Reduced energy efficiency: Battery life drops or data center cooling costs skyrocket.

- Reliability failures: The dreaded Blue Screen or hardware bricking that ruins a brand’s reputation.

5. The bottom line: Business impact

For the C-suite, the atomic defect amplification diagram concludes with a sobering reality check. Atomic-scale issues directly dictate:

- Lower yield: Fewer functional chips per wafer means higher costs per unit.

- Higher power budgets: Products that can’t meet green energy standards or mobile battery requirements.

- Reduced competitiveness: A product that is slower, hotter and less reliable than the competition is a product that doesn’t sell.

Summary: Connecting the dots

The power of this diagram lies in its ability to connect atomic physics → device physics → chip behavior → system impact. It reminds us that in the semiconductor world, there is no such thing as a small problem. Every system-level failure can be traced back to an atomic-level cause, and every atomic-level improvement has the potential to save millions in yield loss.

So in short: How do atomic defects in semiconductors cause business failures?

Atomic defects create interface traps that increase leakage, degrade transistor performance, and reduce reliability. When scaled across billions of devices, these effects lead to lower yield, higher power consumption, thermal throttling, and product failures—directly impacting cost, competitiveness, and brand reputation.

Share

Share

Tweet

Tweet

Share

Share

Share

Share